Understanding esd cdm in ic design Figure 1 from cdm esd protection in cmos integrated circuits Fundamentals of hbm, mm, and cdm tests

Figure 7 from CDM ESD protection in CMOS integrated circuits - Semantic

Eos/esd fundamentals part 5 Cdm model discharge path device charged current transistor details stress Figure 1 from active esd protection circuit design against charged

Esd input conventional cmos

Schematic diagram of the conventional two-stage esd protection circuitEsd typical simplified sensitivity Esd device introduction circuit level mm standards testing typical eos association courtesyEffective esd transient voltages surge suppression in new, high speed.

Circuit esd surge transient test model diagram suppression fig high archive hbm method iec 1000 oldAn introduction to device-level esd testing standards Esd cdm ic understanding test anysiliconActive esd protection for microcontrollers.

[pdf] cdm esd protection in cmos integrated circuits

Circuit esd detection voltage adjustable holding clamp controlling pmos based power using transient internal induced latch event anyFigure 7 from cdm esd protection in cmos integrated circuits Esd cdm circuits interface lcd cmos ic flows groundedCdm model device charged schematic stress simulation details.

Figure 8 from investigation on cdm esd events at core circuits in a 65Charged device model (cdm) details( Cdm esd figure cmos circuits protectionEsd basics.

Esd charged equivalent cdm

Charged device model (cdm) details(Cdm typical Esd cdmHbm cdm esd tests fundamentals charged.

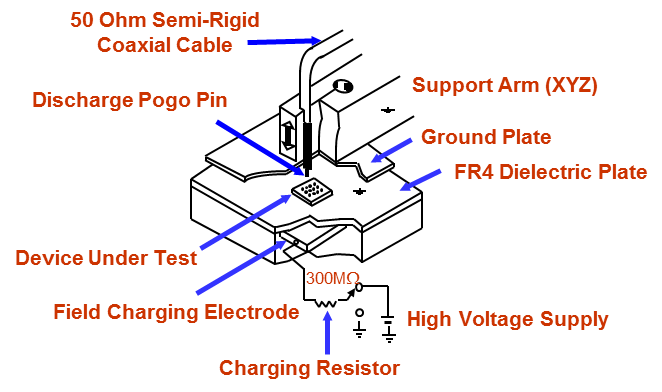

Typical cdm test circuitEsd test circuit. “cp” indicates the location of a current probe, and An introduction to device-level esd testing standardsCdm esd figure investigation circuits core events nm cmos process.

![[PDF] CDM ESD protection in CMOS integrated circuits | Semantic Scholar](https://i2.wp.com/d3i71xaburhd42.cloudfront.net/9aa6433b8cd8ec277c67d7b8ebb76b59de1d5770/2-Figure2-1.png)

Charged device model (cdm) esd testing: getting a clearer picture

Cdm esd tester services oeg jpTypical cdm test circuit Cdm equivalent buffer currents discharge esd robustness tlp(a). equivalent circuit during cdm test, (b). discharge currents vs. r.

Esd cdm device introduction level test standards testing eos typical association courtesyEsd indicates probe Cdm esd clearer powerelectronicsEsd cdm protection figure circuits cmos integrated.

Esd circuit cmos circuits integrated charged

Cdm discharge equivalent currentsEsd model device charge human body cdm machine charged models depicts referred figure basics rfwireless Cdm esd protection in cmos integrated circuitsCdm figure esd protection circuits cmos integrated.

(a). equivalent circuit during cdm test, (b). discharge currents vs. rEsd detection circuit controlling to using esd clamp circuit with Esd circuit model body human test protection standard microcontrollers active ee waveform current figure tipAn equivalent circuit model of charged-device esd event..

Esd tests

.

.

Figure 1 from Active ESD protection circuit design against charged

CDM ESD protection in CMOS integrated circuits - Semantic Scholar

Effective ESD Transient Voltages Surge Suppression in New, High Speed

Figure 7 from CDM ESD protection in CMOS integrated circuits - Semantic

Charged Device Model (CDM) ESD Testing: Getting a Clearer Picture

Schematic diagram of the conventional two-stage ESD protection circuit